Bit Serial Arithmetic In Dsp

In digital logic applications, bit-serial architectures send data one bit at a time, along a single. Bit-serial architectures were developed for digital signal processing in the 1960s through 1980s, including efficient. Arithmetic logic unit (ALU); Address generation unit (AGU); Floating-point unit (FPU); Memory management unit. The input parallel-to serial shift register (PSC) at the input signal sample rate. Figure 3.1: Serial distributed arithmetic FIR filter. As the new sample is serialized, the bit wide output is presented to a bit-serial shift register or time-skew buffer (TSB). The TSB stores the input sample history in a bit-serial format and is used in forming.

Custom Designed Digital Signal Processors Using Bit-Serial Arithmetic LU ( ) • Abstract This thesis presents two prime contributions. First, digital filters for both intermediate and base band filtering for mobile communication are presented. Second, a local clock for on-chip clock generation is introduced. The intermediate frequency filter is a digital alternative to today's analog filters. It is a narrow band filter designed for the American digital mobile telephone system according to the IS-54 specification.

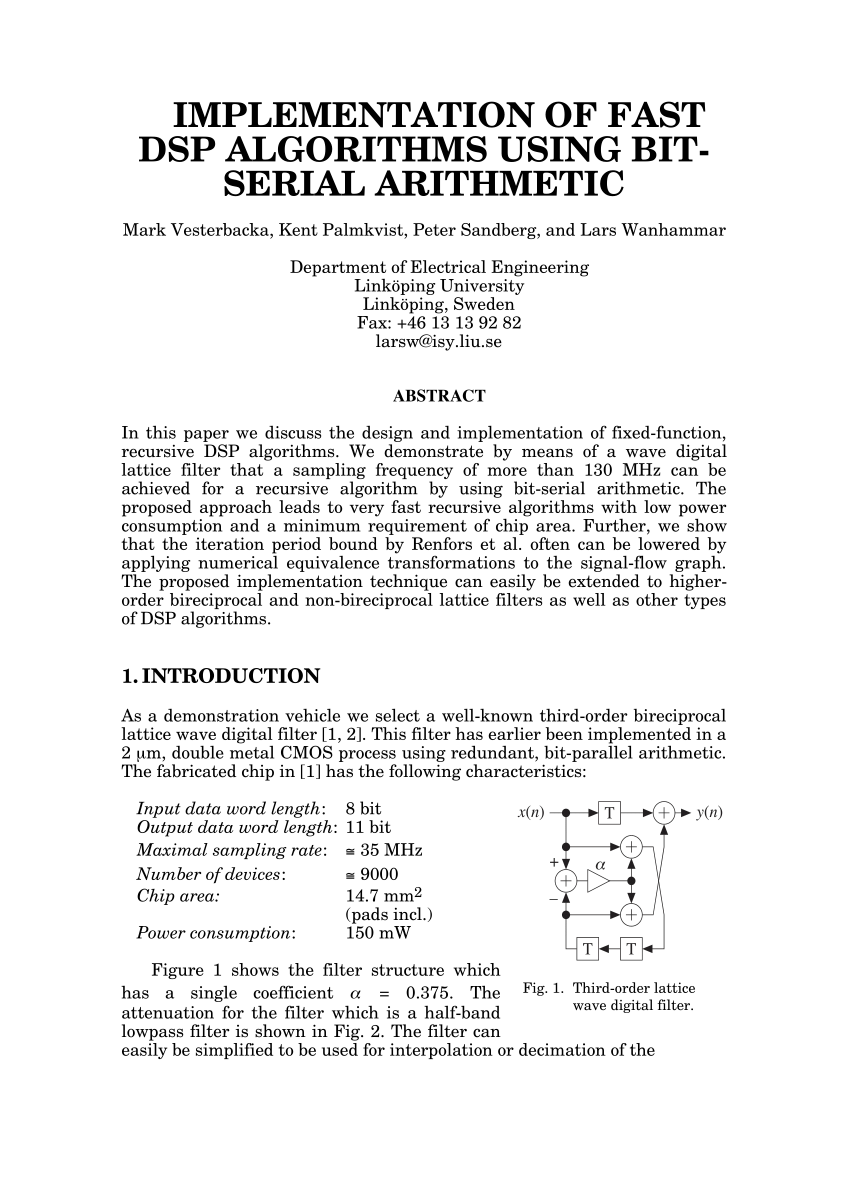

The digital base band filters are designed for use in some wide band research systems. Both the narrow band and the wide band filters use a wave digital lattice structure realized with bit-serial arithmetic. The clock generator is developed to increase the throughput in bit-serial designs such as the intermediate.

This thesis presents two prime contributions. First, digital filters for both intermediate and base band filtering for mobile communication are presented. Second, a local clock for on-chip clock generation is introduced. The intermediate frequency filter is a digital alternative to today's analog filters.

About City Bus Simulator Munich All operational elements of the cab are fully functional. For the first time ever the technical aspects of a bus simulator have been modeled and are based on a real training simulator making the driving characteristics absolutely realistic. The new Citybus Simulator Munich surely sets new standards in terms of graphics for and comes with unique elements making it a fun to play game. The original Munich copilot electronic assistant supports the driver at his daily shift and controls. City bus simulator munich utorrent downloads pc.

It is a narrow band filter designed for the American digital mobile telephone system according to the IS-54 specification. The digital base band filters are designed for use in some wide band research systems.

Both the narrow band and the wide band filters use a wave digital lattice structure realized with bit-serial arithmetic. The clock generator is developed to increase the throughput in bit-serial designs such as the intermediate and the wide band filters above. It is a counter based clock generator i.e the counter stops a ring oscillator after the correct number of cycles has been generated. The generator is a digital alternative to analog on-chip generators as for instance PLL's.

The clock is local and occupies only a small area. Several clock generators can, therefore, be used on the same die. All work presented in this thesis is fabricated and tested in a standard 5 volt CMOS processes. The IS-54 filter is a a twelfth order narrow band filter with 20 kHz band width and a center frequency of 95 kHz.

The wide-band filters are designed for two different systems; the first system is designed for 20 MHz modulated band width and the second is designed for 2 MHz modulated band width. The clock generator is used in all the filter designs and it is also tested separately in a 385 MHz clock generator.

The power consumption is low. Another more important property with respect to the power consumption is that the clock generator is suitable for low supply voltage applications. The on-chip clock generator has been tested down to 0.7 volts in a standard 5 Volts CMOS process. Author LU supervisor • opponent • Professor Aaserud, Odvar, NTH organization • • publishing date 1996 type Thesis publication status published subject • keywords,,,,,,,, pages 157 pages publisher Department of Electroscience, Lund University defense location Room 1406, E-house, at Lund University defense date 1996-05-24 10:15 external identifiers • other:LUTEDX/(TETE--1016)/1--171(1996) language LU publication? Yes id fbd9b7fa-9851-4eed-8a6d-f08431e4a99c (old id 17620) date added to LUP 2007-05-24 09:34:41 date last changed 2018-11-21 21:09:48.